# **Combinational Circuits**

Carmi Merimovich

The Academic College of Tel-Aviv

January 29, 2025

Transistors

n-ary Gates

Circuits

Seven segment

mod 3

lalf adder

Bits Adder

ıll adder

inary adder

Boolean functions (Platonic world)

Combinational circuits (Real hardware)

### Combinational Circuits

${\mathbb C}\,\mathsf{C}.\mathsf{M}.$

### Theme

Transistors

Gates

n-ary Gates

Circuits

Seven segment

mod 3

iaii addei

2-Bits Adde

ull adder

Binary adder

# Realizing the Boolean Operators

## **Switches**

- A switch is a component having three tips -- --

- ► One conrol pin

- ▶ Two data pins

- A switch can be in one of two states

- ▶ Unpressed • • • The control is at logic 0

- The data pins can be in one of two states

- ► Connected --- ---

- Naming and drawing convention:

- ▶ N-switch • Connected ⇔ Pressed

- ▶ P-switch 📤: Connected ⇔ Unpressed

i neme

Transistors

Gates

n-ary Gates

ircuits

Seven segment

nod 3

Half adder

2-Dits Adde

ull adder

# Switch Drawings

| Type       | N             | Р    |

|------------|---------------|------|

| Unpressed  | 0             | 0    |

| switch     |               | ملہ  |

| Pressed    | 1             | 1    |

| switch     | <del></del> - | 00   |

| Bipoloar   | _L            | _L   |

| transistor |               | _/ \ |

| FET        | <u></u>       |      |

| transistor |               |      |

Used in drawings

$Switches \equiv Transistors$

Theme

Transistors

atoc

n-ary Gates

even segment

od 3

alf adde

Bits Adder

ıll adder

The following implementation of logic gates is an abstraction of the CMOS technology. The CMOS technology was invented at Fairchild Semiconductor by Frank Wanlass and Chih-Tang Sah.

### **CMOS**

Complementary Metal-Oxide-Semiconductor

I heme

Transistors

~...

n-ary Gate

ircuits

won coamo

. . . .

ou 5

lalf adder

-Bits Adder

ull adder

## Gates

n-ary Gates

#### ircuits

Seven segment

mod 3

ait adder

Bits Adder

II adder

inary adder

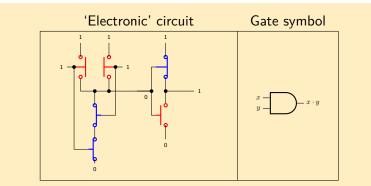

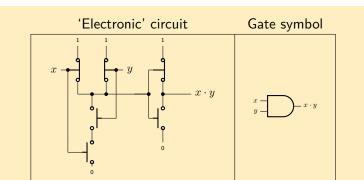

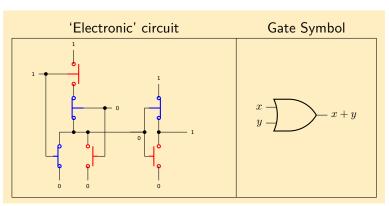

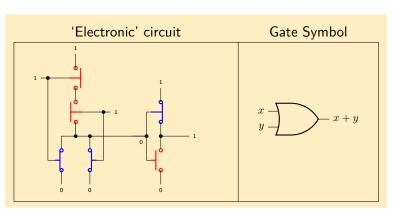

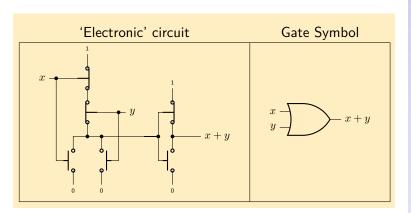

# Logic Gates

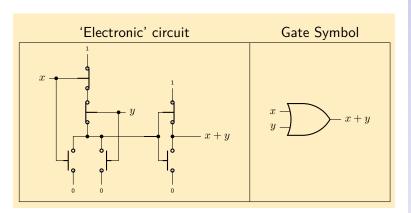

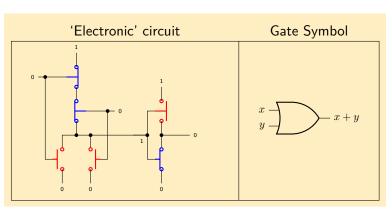

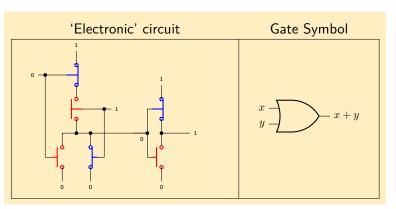

Realizing the Operators  $\cdot,\,+$  and  $^-$

Later on we will see that there are more gates

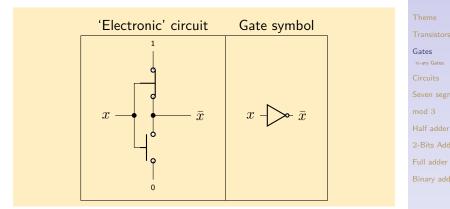

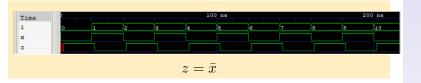

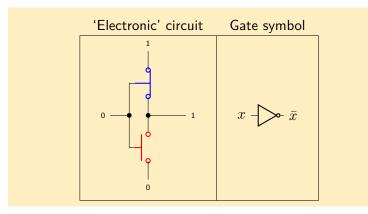

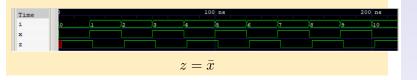

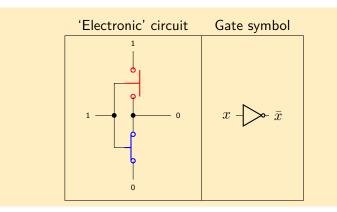

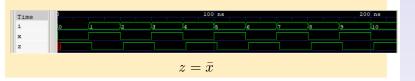

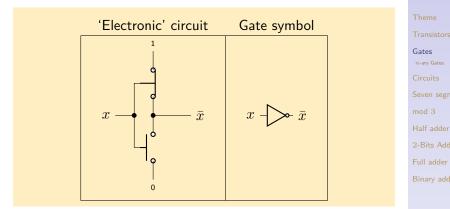

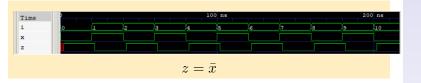

## Not Gate

# Not Gate x = 0

Transistors

Gates

n-ary Gates

Circuits

Seven segment

mod 3

Half adder

2-Bits Adder

Full adder

Binary adder

## Not Gate x = 1

Theme

Transistors

Gates

n-ary Gates

Circuits

Seven segment

mod 3

Half adder

2-Bits Adder

Full adder

## Not Gate

Transistors

### Gates

n-ary Gates

ircuits

Seven segment

od 3

alf add

-Dits Adde

II adder

Transistors

### Gates

n-ary Gates

ircuits

even segmen

od 3

alf adder

-Bits Adde

ıll adder

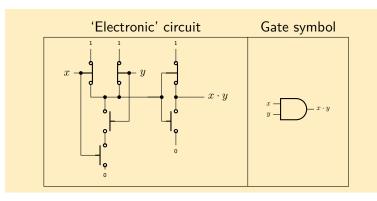

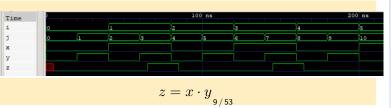

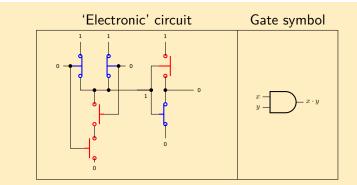

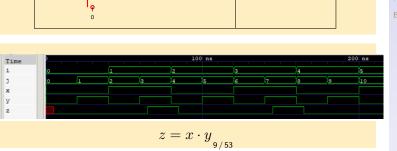

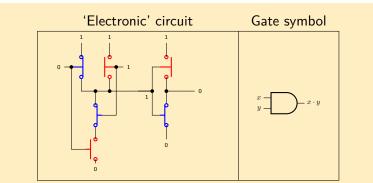

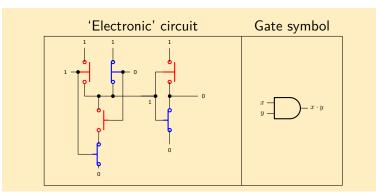

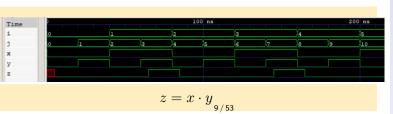

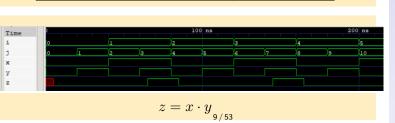

# And Gate x = 0, y = 1

Combinational Circuits

© C.M.

Transistors

## Gates

n-ary Gates

Circuits

even segment

od 3

alf adder

-Bits Adde

ıll adder

Binary adder

Transistors

### Gates

$n ext{-ary Gates}$

Circuits

even segment

od 3

alf adder

-Bits Adde

ıll adder

Transistors

### Gates

n-ary Gates

~:.....:<u>\*</u>...

.

even segment

od 3

alf adde

-Bits Adder

ıll adder

### Gates

#### I heme

Transistors

### Gates

n-ary Gates

#### Circuits

Seven segment

mod 3

Half add

2-Bits Adde

ll adder

#### Theme

Transistors

#### Gates

n-ary Gates

#### Circuits

even segment

#### mod 3

Half adde

2-Dits Adde

ull adder

Transistors

### Gates

n-ary Gates

Circuits

even segment

mod 3

i iaii addei

- .. ..

Transistors

### Gates

n-ary Gates

#### Circuits

even segment

#### mod 3

Half adde

ıll adder

### Gates

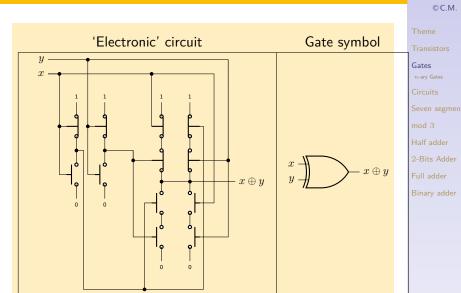

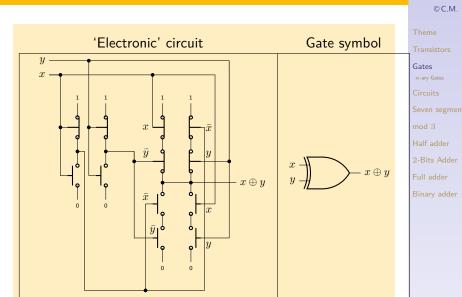

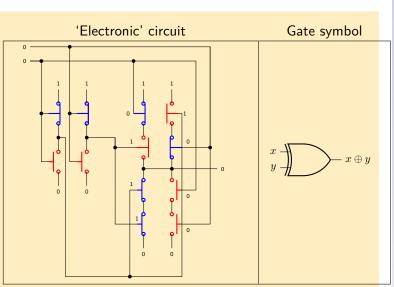

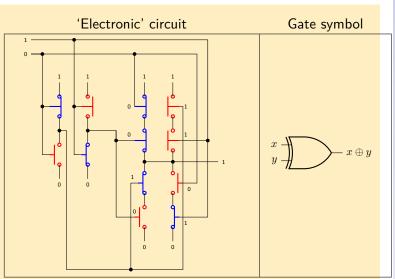

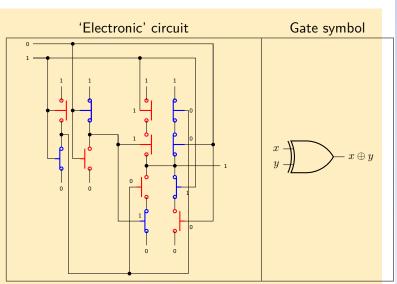

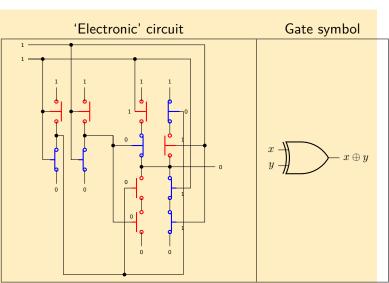

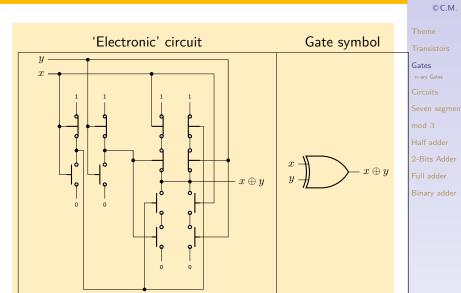

# Xor gate (good place as any)

# Xor gate

Transistors

Gates

$n ext{-ary Gates}$

n ury cutes

ircuits

ven segment

od 3

alf adder

Bits Adder

ıll adder

# $\text{ Xor gate } x = 0, \quad y = 1$

Theme

Transistors

Gates

n-ary Gates

.....

even seamer

. .

od 3

alf adder

Dita Addar

ıll adder

Transistors

Gates

n-ary Gates

ircuite

even segme

od 3

alf adder

-Bits Adder

ıll adder

Transistors

Gates

$n ext{-ary Gates}$

.....

.....

. .

all adder

ıll adder

# Xor gate (good place as any)

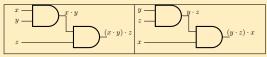

# Commutativity and Associativity

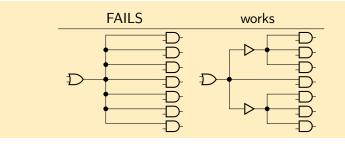

- ullet  $\cdot$ , + and  $\oplus$  are commutative: Gate inputs are symmetric

- $\bullet$  ·, + and  $\oplus$  are associative: Gatewise we get, e.g.,

Or we can use gate with three inputs, e.g.,

- There is a performance **hit** for each additional input pin

- Usually, two successive gate are slower

Theme

Transistors

Gates

-ary Gates

Circuits

Seven segment

nod 3

Half adder

2-Dits Adde

ull adder

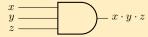

# Multi Inputs Gates

| And gate | $x_0$ $x_0$ $x_0$ $x_0$ $x_0$ $x_0$  |

|----------|--------------------------------------|

| Or gate  | $x_0$ $x_0 + \cdots + x_n$           |

| Xor gate | $x_0$ $x_0 \oplus \cdots \oplus x_n$ |

• Most technologies allow at most 5 input pins

heme

Fransistors

Gates

n-ary Gates

ircuits

Seven segmen

nod 3

lalf adder

. Ditto / taa

ull adder

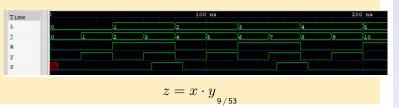

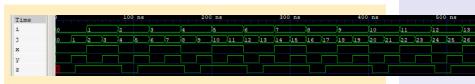

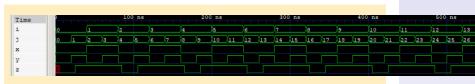

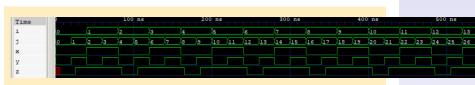

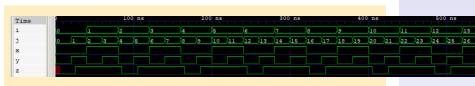

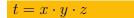

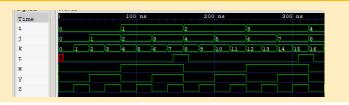

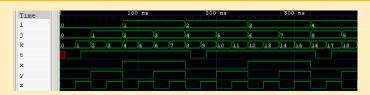

# 3-Inputs Gates waveforms

© C.M.

## t = x + y + z

heme

ransistors

Gates

n-ary Gates

rcuits

even segment

od 3

lalf adde

ull adder

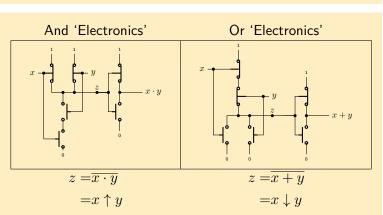

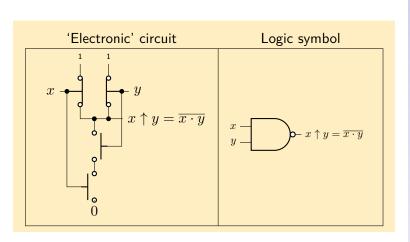

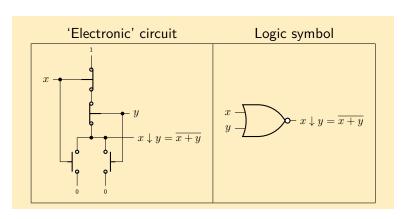

# 'Electronics' observation regarding gates

The realization of both  $\bigcirc$  and  $\bigcirc$  have  $\triangleright$  at their end

Theme

Transistors

### Gates

n-any Gates

rcuits

Beven segment

od 3

lalf adde

-Bits Adder

ıll adder

# Nand $(\uparrow)$ and Nor $(\downarrow)$ Properties

| Nand                                            | Nor                                             |

|-------------------------------------------------|-------------------------------------------------|

| $\bar{x} = \overline{x \cdot x} = x \uparrow x$ | $\bar{x} = \overline{x+x} = x \downarrow x$     |

| $x \cdot y = \overline{\overline{x \cdot y}} =$ | $x \cdot y = \overline{\overline{x \cdot y}} =$ |

| $=\overline{x \uparrow y} =$                    | $=\overline{\bar{x}+\bar{y}}=$                  |

| $= (x \uparrow y) \uparrow (x \uparrow y)$      | $=(x\downarrow x)\downarrow (y\downarrow y)$    |

| $x + y = \overline{\overline{x + y}} =$         | $x + y = \overline{\overline{x + y}} =$         |

| $=\overline{\bar{x}\cdot\bar{y}}=$              | $=\overline{x\downarrow y}=$                    |

| $= (x \uparrow x) \uparrow (y \uparrow y)$      | $=(x\downarrow y)\downarrow (x\downarrow y)$    |

Theme

Transistors

### Gates

n-ary Gates

#### rcuits

Seven segment

#### od 3

Half add

#### 2-Bits Adder

ull adder

# Complete System

### Definition

A set of functions and constants is a complete system if every boolean function can be defined with them

# Corollary

Both  $\{\uparrow\}$  and  $\{\downarrow\}$  are complete systems.

Theme

Transistors

Gates

$n ext{-ary Gates}$

ircuits

even segment

od 3

alf adder

Diag Adday

ull adder

#### Gates

Theme

Transistors

#### Gates

n-any Gate

rcuits

even segment

od 3

lalf adde

| Gate              | Nand                                                                                                                       | Nor                                                                                                                                                                    |

|-------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| x — — — $\bar{x}$ | $x \uparrow x = \bar{x}$                                                                                                   | $x \rightarrow x \downarrow x = \bar{x}$                                                                                                                               |

|                   | $\begin{array}{c c} x & & \\ y & & \\ \end{array}$                                                                         | $x - (x \downarrow x) \downarrow \\ y - (y \downarrow y) = \\ x \cdot y$                                                                                               |

| x - y - x + y     | $\begin{array}{c} x \\ y \\ \end{array} \begin{array}{c} (x \uparrow x) \uparrow \\ (y \uparrow y) = \\ x + y \end{array}$ | $ \begin{array}{c} x \longrightarrow \\ y \longrightarrow \\ \end{array} $ $ \begin{array}{c} (x \downarrow y) \downarrow \\ (x \downarrow y) = \\ x + y \end{array} $ |

Realization of XOR should be here

#### Gates

#### Two final gates

• The buffer gate (important in real circuits):

• The nxor gate:

$$x + y \Rightarrow \overline{x \oplus y}$$

Theme

ransistors

Gates

n-ary Gates

Circuits

even segme

an adder

#### Multi Inputs Variants

#### Associative complement

| Nand gate | $x_0$ $x_0$ $x_0$ $x_0$ $x_0$ $x_0$ $x_0$ |

|-----------|-------------------------------------------|

| Nor gate  | $x_0$ $x_0 + \cdots + x_n$                |

| Nxor gate | $x_0$ $x_0 \oplus \cdots \oplus z$        |

Theme

ransistors

ates

$n ext{-ary Gates}$

ircuits

Seven segment

mod 3

alf adder

, Ditto / taac

ull adder

# (Carmi) Lecture 6 reached here

Combinational Circuits

${\mathbb C}\,\mathsf{C.M.}$

Them

Transistor

n-ary Gates

Circuits

Seven segment

mod 3

Half add

2-Bits Adder

ull adder

#### Combinational Circuits

${\mathbb C}\,\mathsf{C}.\mathsf{M}.$

i neme

ransistors

Jaccs

n-ary dates

Circuits

Seven segment

mod 3

an adder

Bits Adder

ıll adder

nary adder

#### **Combinational Circuits**

(Realization of boolean functions)

Recall that the booean operators are boolean functions

#### Functions to be Realized

Combinational Circuits

©C.M.

- Seven Segment

- mod 3

- Half adder

- 2-bit binary adder

- Full adder

- Binary adder

The boolean functions are from the previous chapter

heme

Transistors

- --- C-t--

n-ary Gates

Circuits

Seven segment

mod 3

Half add

-Bits Adder

-ull adder

#### Combinational Circuits

©C.M.

Seven segment

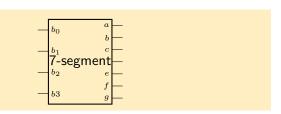

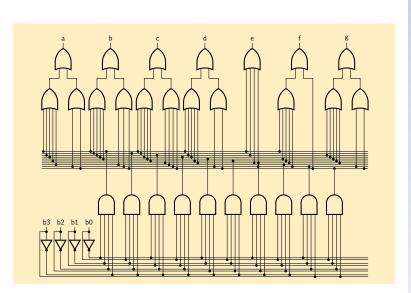

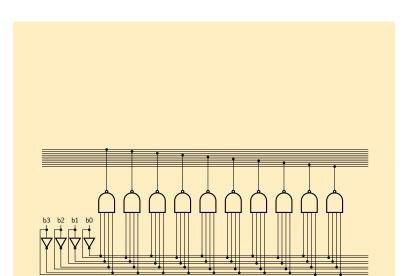

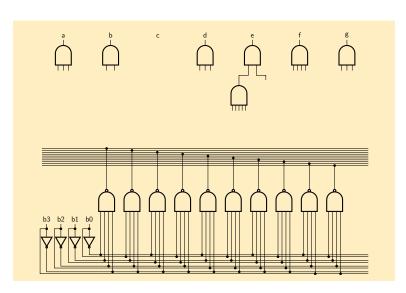

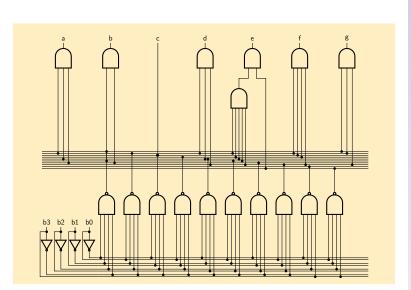

### Realizing the Seven-Segment

The formuale are from the previous lecture

- 1. Block diagram

- 2. Logic circuit

### Seven-Segment (block diagram)

Combinational Circuits

${\mathbb C}\,\mathsf{C}.\mathsf{M}.$

Theme

ransistors

Gates

n-ary Gates

ircuits

Seven segment

nod 3

alf adder

-Bits Adder

ull adder

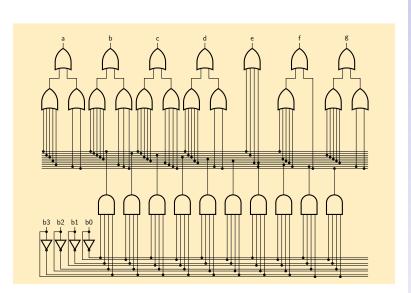

### Seven-Segment (formulae)

| <u>SOP</u>                                                | <u>POS</u>                                              |                   | Т      |

|-----------------------------------------------------------|---------------------------------------------------------|-------------------|--------|

| $a = m_0 + m_2 + m_3 + m_5 + m_7 + m_8 + m_9$             | $a = \bar{m}_1 \bar{m}_4 \bar{m}_6$                     |                   |        |

| $b = m_0 + m_1 + m_2 + m_3 + m_4 + m_7 + m_8 + m_9$       | $b = \bar{m}_5 \bar{m}_6$                               |                   | G      |

| $c = m_0 + m_1 + m_3 + m_4 + m_5 + m_6 + m_7 + m_8 + m_9$ | $c = \bar{m}_2$                                         |                   |        |

| $d = m_0 + m_2 + m_3 + m_5 + m_6 + m_8$                   | $d = \bar{m}_1 \bar{m}_4 \bar{m}_7$                     |                   |        |

| $e = m_0 + m_2 + m_6 + m_8$                               | $e = \bar{m}_1 \bar{m}_3 \bar{m}_4 \bar{m}_5 \bar{m}_7$ | $\bar{m}_{arphi}$ | 5<br>9 |

| $f = m_0 + m_4 + m_5 + m_6 + m_8 + m_9$                   | $f = \bar{m}_1 \bar{m}_2 \bar{m}_3 \bar{m}_7$           |                   | n      |

| $g = m_2 + m_3 + m_4 + m_5 + m_6 + m_8 + m_9$             | $g = \bar{m}_0 \bar{m}_1 \bar{m}_7$                     |                   | H      |

|                                                           |                                                         |                   | 2      |

Theme

Fransistors

Gates

n-ary Gates

Circuits

Seven segment

mod 3

alf adder

-Dits Adde

-ull adder

#### Combinational Circuits © C.M.

## Seven Segment (SOP)

Theme

±.....

m any Cate

n-ary Gates

ircuits

Seven segment

mod 3

iaii adde

-Bits Adder

ull adder

Combinational Circuits

©C.M.

Theme

Transistors

Gates

n-ary Gates

Seven segment

lalf adder

2-Bits Adde

ull adder

Combinational Circuits

©C.M.

Theme

ransistors

m any Cates

..., .....

Seven segment

1.0

- ...

ull adder

©C.M.

Theme

Transistors

n-any Gates

....

Seven segment

nod 3

Half add

-Bits Adder

-ull adder

Combinational Circuits

© C.M.

Theme

Transistors

aates

Seven segment

mod 3

Half add

2-Bits Adder

ull adder

Combinational Circuits

© C.M.

Theme

Transistors

Gates

n-ary Gates

ircuits

Seven segment

mod 3

Half add

2-Bits Addei

ull adder

Combinational Circuits

©C.M.

Theme

**Fransistors**

Mates

ircuits

Seven segment

mod 3

Half add

2-Bits Adde

ull adder

${\mathbb C}\,\mathsf{C}.\mathsf{M}.$

I heme

**Transistors**

Cates

.. .., .....

on cares

Seven segment

mod 3

наіт афф

2-Bits Adder

-ull adder

Combinational Circuits © C.M.

Transistors

C-+--

n-ary Gate

ircuits

Seven segment

mod 3

наіт афф

2-Bits Adde

Full adder

#### Combinational Circuits © C.M.

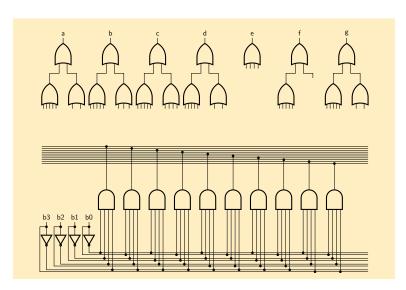

## Seven Segment (SOP)

Theme

Transistors

Gates

n-ary Gate

ircuits

Seven segment

mod 3

-Bits Adder

ull adder

#### Combinational Circuits © C.M.

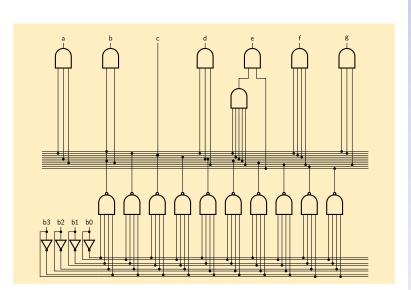

## Seven Segment (POS)

Theme

\_ . . .

m any Cate

n-ary Gates

ircuits

Seven segment

$\mod 3$

Half add

2-Bits Adde

ull adder

Combinational Circuits

©C.M.

Theme

Transistors

ates

ı-ary Gates

ircuits

Seven segment

nod 3

ait adder

\_\_\_\_\_

ull adder

Combinational Circuits

©C.M.

Theme

ransistors

ates

nt-ary Gates

Seven segment

mod 3

Half add

ull adder

${\mathbb C}\,\mathsf{C}.\mathsf{M}.$

Theme

Transistors

n-ary Gates

· .

Seven segment

mod 3

Hait adder

. Dies / lade

ull adder

Combinational Circuits

©C.M.

Theme

Transistors

m any Cates

.. .., .....

Seven segment

seven segment

nou 5

наіт афф

2-Bits Addei

ull adder

Combinational Circuits

© C.M.

Theme

Transistors

Gates

n-ary Gates

-----

Seven segment

mod 3

Half add

2-Bits Adde

ull adder

Combinational Circuits

©C.M.

Transisto

Gates

n-ary Gates

Circuits

Seven segment

mod 3

Half add

2-Bits Adde

ull adder

Combinational Circuits

${\mathbb C}\,\mathsf{C}.\mathsf{M}.$

I heme

Transistors

Gates

n-ary Gates

Circuits

Seven segment

mod 3

Half add

2-Bits Adder

Full adder

Combinational Circuits © C.M.

Theme

Transistors

Catac

n-ary Gates

ircuits

Seven segment

mod 3

Half add

2-Bits Adde

-ull adder

#### Combinational Circuits © C.M.

## Seven Segment (POS)

Theme

\_ . . .

m any Cate

n-ary Gates

ircuits

Seven segment

$\mod 3$

Half add

2-Bits Adde

ull adder

# Combinational Circuits © C.M.

Theme

Transistors

Gates

n-ary Gates

rcuits

Seven segment

$\mod 3$

air adder

-Bits Adde

Full adder

inary adder

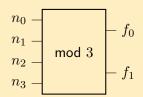

## Realizing mod 3

The formuale are from the previous lecture

- 1. Block diagram

- 2. Logic circuit

#### Combinational Circuits © C.M.

mod 3 Block Diagram

Theme

Transistors

Jates

n-ary Gates

ircuits

even segment

$\bmod\ 3$

all adder

Bits Adder

ull adder

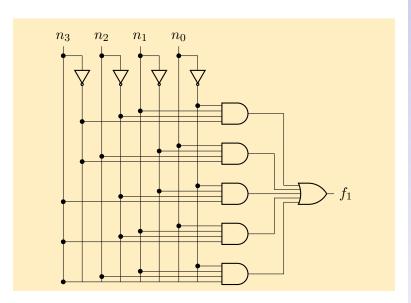

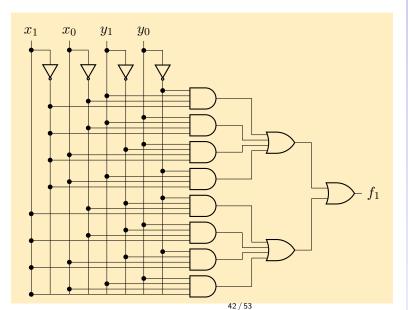

$$f_1 = \bar{n}_3 \bar{n}_2 n_1 \bar{n}_0 + \bar{n}_3 n_2 \bar{n}_1 n_0 + n_3 \bar{n}_2 \bar{n}_1 \bar{n}_0 + n_3 \bar{n}_2 n_1 n_0 + n_3 n_2 n_1 \bar{n}_0$$

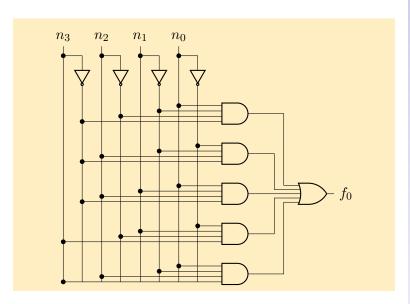

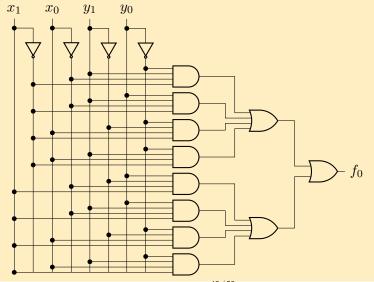

$$f_0 = \bar{n}_3 \bar{n}_2 \bar{n}_1 n_0 + \bar{n}_3 n_2 \bar{n}_1 \bar{n}_0 + \bar{n}_3 n_2 n_1 n_0 + n_3 \bar{n}_2 n_1 \bar{n}_0 + n_3 n_2 \bar{n}_1 n_0$$

Theme

Transistors

Gates

n-ary Gates

.....

even segment

$\bmod \ 3$

iaii addci

.. ..

#### $mod 3 f_1$ -Circuit

Theme

ransistors

Gates

n-ary Gates

ircuits

Seven segment

$\bmod\ 3$

hali addei

2-Bits Adder

ull adder

## $\mod 3$ $f_0$ -Circuit

Theme

Transistors

Gates

n-ary Gates

ircuits

seven segment

$\bmod \ 3$

Half add

2-Bits Adder

ull adder

#### Combinational Circuits ©C.M.

Half adder

## Realizing the Half Adder

The formuale are from the Boolean Algebra lecture

- 1. Block diagram

- 2. Logic circuit

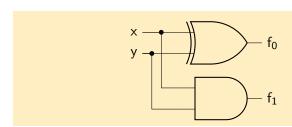

#### Half Adder (previous lecture)

$$f_1 = x \cdot y$$

$$f_0 = x \oplus y$$

#### Two bits in, two bits out

#### I heme

ransistors

#### ates

n-ary Gates

#### Circuits

even segment

#### nod 3

Half adder

#### Dire Address

Full adder

Theme

Transistors

ates

-ary Gates

ircuits

Seven segment

nod 3

Half adder

-Bits Adder

ull adder

# Combinational Circuits © C.M.

Theme

Transistors

ates a-ary Gates

6

mod 3

Half adder

2-Bits Adder

-ull adder

Sinary adder

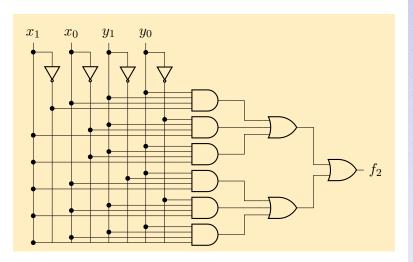

## Realizing 2-Bits Adder

(The formulae are from the Boolean Algebra chapter)

$$f_{2} = \bar{x}_{1}x_{0}y_{1}y_{0} + x_{1}\bar{x}_{0}y_{1}\bar{y}_{0} + x_{1}\bar{x}_{0}y_{1}y_{0} + x_{1}x_{0}\bar{y}_{1}y_{0} + x_{1}x_{0}\bar{y}_{1}y_{0} + x_{1}x_{0}y_{1}\bar{y}_{0} + x_{1}x_{0}y_{1}y_{0}$$

$$f_{1} = \bar{x}_{1}\bar{x}_{0}y_{1}\bar{y}_{0} + \bar{x}_{1}\bar{x}_{0}y_{1}y_{0} + \bar{x}_{1}x_{0}\bar{y}_{1}y_{0} + \bar{x}_{1}x_{0}y_{1}\bar{y}_{0} + x_{1}x_{0}\bar{y}_{1}\bar{y}_{0} + x_{1}x_{0}y_{1}y_{0} + x_{1}x_{0}y_{1}\bar{y}_{0} + x_{1}x_{0}y_{1}\bar{y}_{0} + \bar{x}_{1}\bar{x}_{0}y_{1}y_{0} + \bar{x}_{1}x_{0}y_{1}\bar{y}_{0} + \bar{x}_{1}x_{0}y_{1}\bar{y}_{0} + x_{1}\bar{x}_{0}y_{1}\bar{y}_{0} + x_{1}\bar{x}_{0}y_{1}\bar{y}_{0} + x_{1}\bar{x}_{0}y_{1}\bar{y}_{0} + x_{1}\bar{x}_{0}y_{1}\bar{y}_{0} + x_{1}x_{0}y_{1}\bar{y}_{0}$$

I heme

ransistors

Gates

n-ary Gates

ircuits

even segment

od 3

Half adde

2-Bits Adder

ull adder

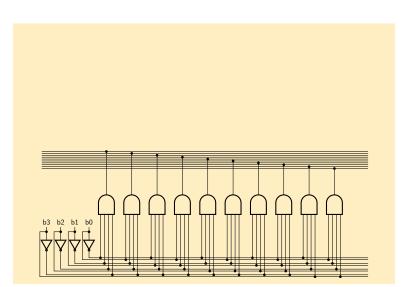

### 2-Bits Adder $f_2$ -Circuit

Theme

Transistors

n-ary Gates

even segme

od 3

lalf adde

2-Bits Adder

ull adder

## 2-Bits Adder $f_1$ -Circuit

Combinational Circuits © C.M.

heme

Transistors

Gates

n-ary Gates

. .

Savan sa

seven segn

ا الدامالا

2-Bits Adder

Full addan

# 2-Bits Adder $f_0$ -Circuit

Combinational Circuits © C.M.

Transistors

Gates

$n ext{-ary Gates}$

ircuite

Seven seg

nod 3

Half add

2-Bits Adder

ull adder

# Realizing the Full Adder

Formuale are from the boolean algebras lecture

- 1. Block diagram

- 2. Logic circuit

#### Combinational Circuits

${\mathbb O}\,\mathsf{C.M.}$

i neme

Transistor

Jaces .

n-ary Gates

ircuits

Seven segment

mod 3

lalf adder

Rits Adder

Full adder

$$f_0(x, y, z) = x \oplus y \oplus z$$

$$f_1(x, y, z) = \bar{x}yz + x\bar{y}z + xy\bar{z} + xyz =$$

$$= (x + y + z)(x + y + \bar{z})(x + \bar{y} + z)(\bar{x} + y + z) =$$

$$= yz + xz + xy$$

Transistors

n-ary Gates

ircuite

Seven segment

mod 3

Half adde

2-Bits Adder

Full adder

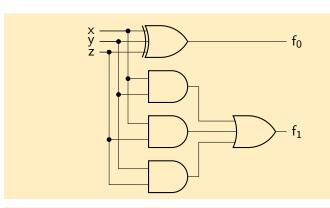

## Full adder ( $f_1$ SOP)

$$f_0(x, y, z) = x \oplus y \oplus z$$

$$f_1(x, y, z) = \bar{x}yz + x\bar{y}z + xy\bar{z} + xyz$$

#### Theme

Transistors

Cates

n-ary Gates

.....

even segment

100 3

lalf adde

2-Bits Adder

Full adder

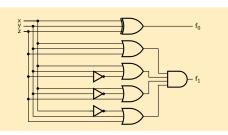

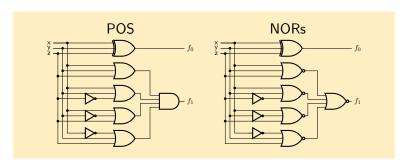

## Full adder ( $f_1$ POS circuits)

$$f_0(x, y, z) = x \oplus y \oplus z$$

$f_1(x, y, z) = (x + y + z)(x + y + \bar{z})(x + \bar{y} + z)(\bar{x} + y + z)$

#### . . . . . .

Transistors

$n ext{-ary Gates}$

ircuits

Seven segment

100 3

iait adder

-Bits Adder

Full adder

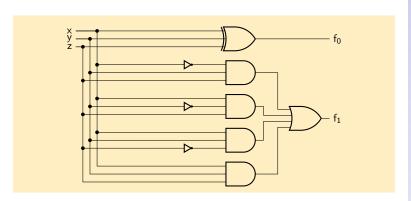

## Full adder (simplified circuit)

$$f_0(x, y, z) = x \oplus y \oplus z$$

$$f_1(x, y, z) = yz + xz + xy$$

Theme

**-** ...

n-ary Gates

ircuits

Seven segme

even segment

nod 3

lalf adde

-Bits Adder

Full adder

Theme

Transistors

atoc

$n ext{-ary Gates}$

even segmen

mod 3

lalf adde

-Bits Adder

Full adder

$$f_0(x, y, z) = x \oplus y \oplus z$$

$f_1(x, y, z) = (x + y + z)(x + y + \bar{z})(x + \bar{y} + z)(\bar{x} + y + z)$

Toologichaus

Gates

n-ary Gates

rcuits

even segment

od 3

Half adde

2-Bits Adder

Full adder

#### Combinational Circuits © C.M.

Theme

Transistors

Gates

n-ary Gates

ircuits

seven segment

mod 3

iaii adder

ull adder

Binary adder

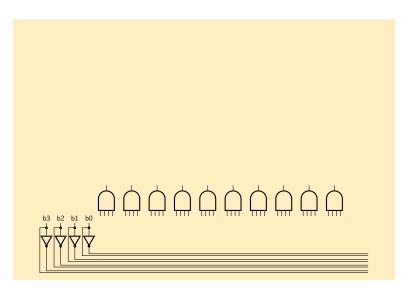

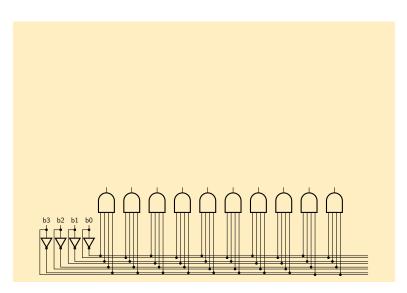

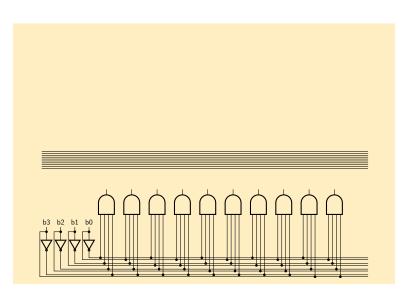

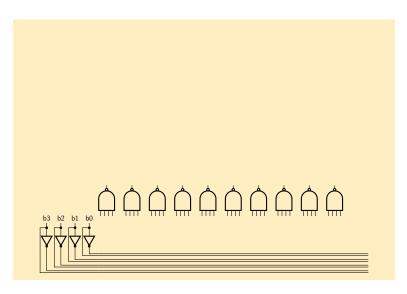

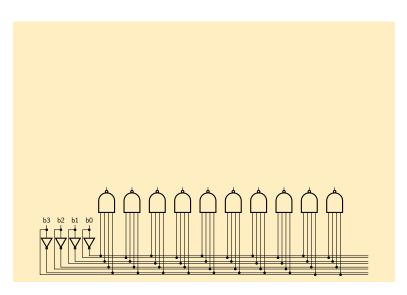

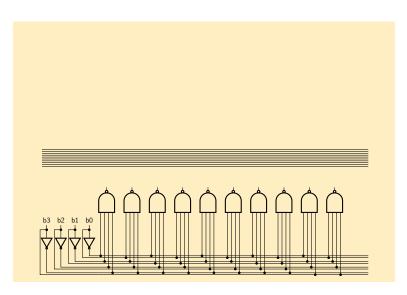

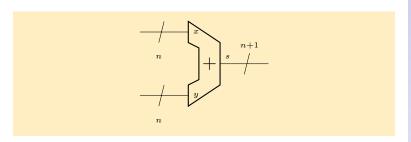

## Realizing the Binary Adder

The formuale are from the previous lecture

- 1. Block diagram

- 2. Logic circuit

# Binary adder (block diagram)

Theme

ransistors

ates

n-ary Gates

rcuits

Seven segment

nod 3

iaii auuei

-bits Adder

Full adder

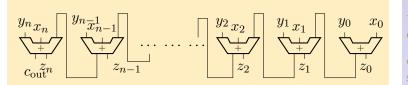

## Binary Adder (circuit)

Theme

Transistors

Sates

n-ary Gates

cuits

even segm

nod 3

alf adder

2-Dits Addi

ull adder