© Carmi Merimovich

January 29, 2025

#### The General Problem

Cache

©C.M.

Read (scheme)

irect Mapping

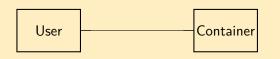

- The container is large and slow

- The user is very fast

- The user has 'locality of reference'

#### Solution

Cache

©C.M.

Direct Manning

irect iviapping

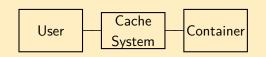

- The cache is **faster** than the container

- The cache holds relatively a small amount of data

- Temporarily, the cache holds replicas of popular data

- (Thus, per bit, the cache is more expensive)

Without locality of reference the cache is useless

## Key

Cache ©C.M.

Direct Mapping

Each item in the container has an address.

- The user uses this address to read/write the item

- This must **not** change with the addition of the cache

- Thus the cache needs to use the address as a key

## The Dictionary Data Structure

Cache

©C.M.

Read (scheme)

irect Mapping

| key1 | value1 |  |

|------|--------|--|

| key2 | value2 |  |

| :    | :      |  |

|      |        |  |

| i    | :      |  |

| :    | :      |  |

• Hardwarewise, dictionary is 'associative memory'

#### The Cache

Cache

©C.M.

Direct Manning

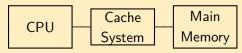

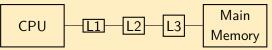

Classically the cache is an SRAM unit sitting between the CPU and the main memory

However, nowadays we have a sequence of caches

L4 cache is not unheard of (as of 2023)

### All (most) cahches today are on the CPU die

In the olden days, the (one) cache was farther away

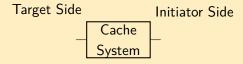

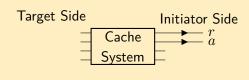

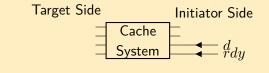

## Target/Initiator Sides

Cache

©C.M.

Read (scheme)

Direct Mapping

- Note the cache talks with buses

- So, in princple, it does not know who sits on the other side of the bus

- Most cache operations are indifferent to positioning

Single, L1,L2,L3

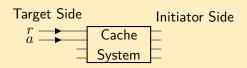

- For a uniform discussion we use the following:

©C.M.

Read (scheme)

irect Mapping

## Read Command to the Cache

Read is simple. No variants.

#### Read and Hit

Cache

©C.M.

Read (scheme)

irect Mapping

#### Item found in cache memory

### Data sent to faster system

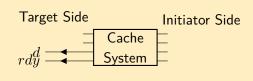

## Read and Miss (1)

Cache

©C.M.

Read (scheme)

irect Mapping

#### Item is not in cache memory

## Request passed to slower system

## Read and Miss (2)

Cache

©C.M.

Read (scheme)

## Data received from slower system

## Item is saved in the Cache Memory

This might lead to some other item to be evicted

### Data sent to faster system

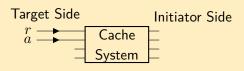

#### Notes on Read

Cache

©C.M.

Read (scheme)

Direct Mapping

- Accessing items radomly once will probably yield misses

- Repeatedly accessing an item will probably yield miss followed by hits

- For large blocks, sequential access will also yield miss followe by hits

©C.M.

Read (scheme)

Direct Mapping

# Direct Mapping Cache

Read (scheme)

Direct Mapping

Dir

| • | The | structure | of th | ne cache | memory |

|---|-----|-----------|-------|----------|--------|

|---|-----|-----------|-------|----------|--------|

| tag | block/line | flags |

|-----|------------|-------|

| :   | :          | :     |

- ullet The flags contains at least the Valid flag

- The block size is always  $2^nB$  for some n

- The number of blocks is always  $2^k$  for some k

- The size of the cache is  $2^k \times 2^n B$

- (The tag and flag fields are ignored for size calculations)

- ullet The cache memory has its own addresses:  $0-(2^k-1)$

- We call this address the index

- (This helps us)

©C.M.

Read (scheme)

Direct Mapping